# BOARD TESTING WITH BOUNDARY SCAN: TPG STRATEGY

7th European Design for Testability Workshop - Segóvia, June 1990

José M. M. Ferreira<sup>1</sup>, José S. Matos<sup>1</sup>, Frans de Jong<sup>2</sup>

The work described in this poster was partially funded by the EEC under contract No. ESPRIT 2478.

<sup>1</sup> INESC / Faculty of Engineering, University of Porto - Porto - Portugal

<sup>&</sup>lt;sup>2</sup> Philips CFT - Eindhoven - The Netherlands

## Different testing scenarios present different requirements.

### • Production testing

• Go/no-go testing. Fault diagnosis is not required.

#### • Field maintenance

- Go/no-go testing. Fault diagnosis is not required.

- Self test (either board or system level) is also a go/no-go testing. Only fault detection is required.

### Repairing

- An enhanced diagnosis accuracy is required.

- The smallest replaceable unit must be identifiable without ambiguity.

Several factors must be considered when defining a fault model for Boundary Scan boards.

- The result of a short is an analog value, which must be read by digital means (0 or 1?).

- Open and short faults exhibit a logic behavior which depends on the technology involved, and also on the number of shorted outputs, and their logic levels.

- A fault model must be reevaluated for each new technology, or when different technologies are used in the same board. DFT rules at chip-level may also help (e.g., assuring that floating inputs capture a fixed value).

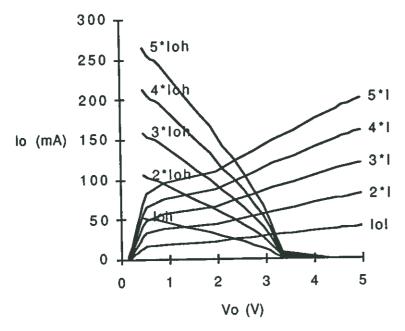

(74LS04)

Result of a short among (one to five) TTL LS outputs.

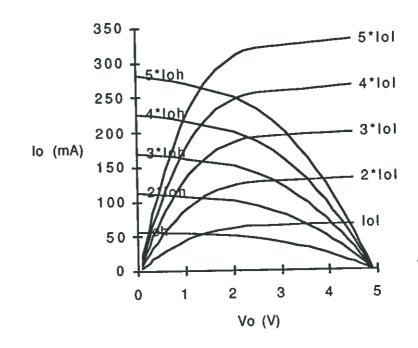

Result of a short among (one to five) BiCMOS outputs. (74BCT8373 BST octal from Texas Instruments)

## Interconnect short fault TPG algorithms:

| net                                                              | Binary Search 1                                                                      | Wagner <sup>2</sup>                                     | Walk. Sequence <sup>3</sup>                                                                                                       | Min. Weight <sup>4</sup>                                                             | Max. Independ. <sup>4</sup>                                                                  |

|------------------------------------------------------------------|--------------------------------------------------------------------------------------|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| n1<br>n2<br>n3<br>n4<br>n5<br>n6<br>n7<br>n8<br>n9<br>n10<br>n11 | 0001<br>0010<br>0011<br>0100<br>0101<br>0110<br>0111<br>1000<br>1001<br>1010<br>1011 | 00011110<br>00101101<br>00111100<br>01001011<br>0101101 | 01111111111<br>10111111111<br>110111111111<br>11101111111<br>11110111111<br>11111011111<br>11111101111<br>11111110111<br>11111111 | 0111<br>1011<br>1101<br>1110<br>0011<br>0101<br>0110<br>1001<br>1010<br>1100<br>0001 | 0111<br>1011<br>1101<br>1110<br>0011<br>1001<br>1100<br>0101<br>1010<br>0001<br>1000<br>0110 |

<sup>1</sup> W. Kautz, Testing for faults in wiring networks, IEEE Transactions on Computers, Vol.C-23, Nº4, April 1974, pp.358-363 P. Goel, M. McMahon, Electronic chip-in-place test, Proceedings of the 13th ITC, 1982, pp.83-90

<sup>2</sup> P. Wagner, Interconnect testing with boundary scan, Proceedings of the 18th ITC, 1987, pp.52-57

<sup>3</sup> A. Hassan, J. Rajski, V. Agarwal, Testing and diagnosis of interconnects using boundary scan architecture, Proceedings of the 19th ITC, 1988, pp.126-137

<sup>4</sup> C. Yau, N. Jarwala, A unified theory for designing optimal test generation and diagnosis algorithms for board interconnects, Proceedings of the 20th ITC, 1989, pp.71-77

Diagnostic accuracy is limited by response ambiguity, which may be described on the basis of aliasing and confounding syndromes 1:

| net                                                              | Applied                                                                                      | Responses                                                                                  |  |

|------------------------------------------------------------------|----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|--|

| n1<br>n2<br>n3<br>n4<br>n5<br>n6<br>n7<br>n8<br>n9<br>n10<br>n11 | 0001<br>0010<br>0011<br>0100<br>0101<br>0110<br>0111<br>1000<br>1001<br>1010<br>1011<br>1100 | 0001 < 0010<br>0001 < 0100 < 0100 < 0100 < 0100 < 1000<br>0101 < 1000<br>1010 1011<br>1100 |  |

Aliasing: Is net n1 shorted to nets n3 and n9?

Confounding: Are (n4,n7) and (n5,n6) two independent shorts?

<sup>&</sup>lt;sup>1</sup> N. Jarwala, C. Yau, A new framework for analyzing test generation and diagnosis algorithms for wiring interconnects, Proceedings of the 20th ITC, 1989, pp.63-70.

## Short-form comparison of one-step TPG algorithms:

| Algorithm                 | Binary Search                             | Wagner                            | Walking Sequence      | Minimum Weight                                                                    | Max. Independence                                                      |

|---------------------------|-------------------------------------------|-----------------------------------|-----------------------|-----------------------------------------------------------------------------------|------------------------------------------------------------------------|

| Num. of TPs               | ceil[log2(N)] <sup>1</sup>                | 2*ceil[log2(N)]                   | N                     | p 2                                                                               | $p=f(E,N)^3$                                                           |

| Applic. time <sup>4</sup> | 9 ms                                      | 18 ms                             | 500 ms                | p ms                                                                              | 24 ms <sup>5</sup>                                                     |

| Diagnosis                 | Poor. Aliasing and confounding may occur. | Poor. Only confounding may occur. | Complete.             | Poor. Better for large values of p.                                               | Complete.                                                              |

| Comments                  | Minimum number of TPs generated.          | Small number of TPs generated.    | Too many TPs geneted. | Vector assignment to<br>nets aims to minimi-<br>ze aliasing and con-<br>founding. | Additional information (PCB layout, process characteristics) required. |

$<sup>\</sup>frac{1}{2}$  ceil[log2(N)] represents the first integer not smaller than log2(N).

<sup>&</sup>lt;sup>2</sup> p is specified by the user

<sup>3</sup> p is given as a function of the maximum short extent (E), and the total number of nets (N).

<sup>4</sup> Approximate values, assuming a circuit with 500 nets, 1000 BS cells, and a 1 MHz TCK.

<sup>5</sup> Assuming a circuit with 1000 BS cells, and a maximum short extent (E) of 20.

## Short-form comparison of adaptive TPG algorithms:

| Algorithm                 | Goel and McMahon                                                                           | Optimal C-test                                                                 |

|---------------------------|--------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| Num. of TPs               | ceil[log2(N)] + W <sup>1</sup>                                                             | $ceil[log2(N)] + C^2$                                                          |

| Applic. time <sup>3</sup> | 9 ms + W ms                                                                                | 9 ms + C ms                                                                    |

| Diagnosis                 | Complete.                                                                                  | Complete.                                                                      |

| Comments                  | A walking sequence is generated over the set of all nets responding with faulty responses. | Reduction on the number of TPs is obtained at the cost of an extra complexity. |

W is the number of nets responding with faulty responses.

C is the maximum number of independent faults in any confounding syndrome (the maximum degree of confounding).

Approximate values, assuming a circuit with 500 nets, 1000 BS cells, and a 1 MHz TCK.

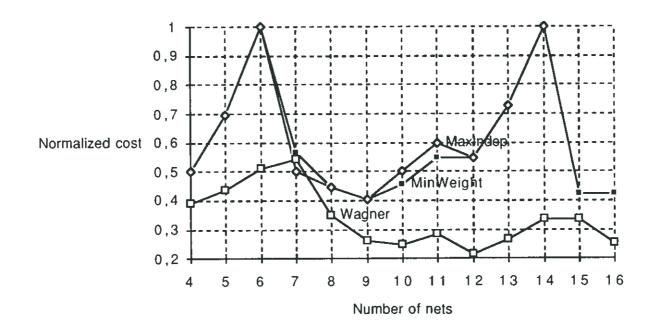

Normalized 1 cost for various TPG algorithms 2: Cost:

sum of the size of all EPSs number of EPSs

<sup>1</sup> The base cost corresponds to the binary search algorithm.

<sup>&</sup>lt;sup>2</sup> The Wagner algorithm requires twice the number of TPs used by the other three algorithms.

How to measure the relative merits of these TPG algorithms, concerning the likelihood of occurrence of ambiguous responses?

- The number of aliasing syndromes is not a significant parameter (only one further TP is needed to solve all aliasing syndromes).

- The number of confounding syndromes is a much more significant parameter. But the task of determining the maximum number of independent faults in each confounding syndrome (the degree of confounding) is too complicated.

On the other hand, an adaptive algorithm using this parameter to generate the second set of TPs requires a complex analysis of the responses obtained in the first step.

A simple and efficient solution skips the determination of the degree of confounding (no checking is done to see whether the fault syndrome is effectively confounding).

Each set of nets responding with the same vector is considered an *Eventually Puzzling Syndrome* (EPS), independently of effectively containing aliasing or confounding syndromes.

Comparison of TPG algorithms may now be done in a more straightforward manner, by using a criterion based on EPSs.

A suitable TPG strategy for the various testing scenarios must then accommodate the following requirements:

- Because diagnostic accuracy is frequently not important, it must be possible to choose between a smaller set of TPs (allowing a faster test) or an enhanced diagnosis capability.

- When diagnostic accuracy is required, a compromise must be found between the number of TPs, and the complexity of the TPG procedure.

A TPG strategy fulfilling these requirements may be defined as follows:

- A two-step adaptive strategy is used. The first step alone is used when fault diagnosis is not required.

- The TPG algorithm used in the first step is the Minimum Weight, with a number of TPs given by ceil [log2(N+2)].

- The TPG algorithm used in the second step is the Walking Sequence, applied to each EPS. Since all EPSs are solved in parallel, the number of TPs is given by the maximum number of nets in any EPS.